Universidad de Murcia Departamento de Ingeniería y Tecnología de Computadores

# Efficient and Scalable Cache Coherence for Many-Core Chip Multiprocessors

A dissertation submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

By Alberto Ros Bardisa

Advisors José Manuel García Carrasco Manuel Eugenio Acacio Sánchez

Murcia, July 2009

Universidad de Murcia Departamento de Ingeniería y Tecnología de Computadores

## Coherencia de Cache Eficiente y Escalable para Multiprocesadores en un Solo Chip

Tesis propuesta para la obtención del grado de Doctor

Autor: Alberto Ros Bardisa

Directores: José Manuel García Carrasco Manuel Eugenio Acacio Sánchez

Murcia, Julio de 2009

D. José Manuel García Carrasco, Catedrático de Universidad del Área de Arquitectura y Tecnología de Computadores en el Departamento de Ingeniería y Tecnología de Computadores

y

D. Manuel Eugenio Acacio Sánchez, Profesor Titular de Universidad del Área de Arquitectura y Tecnología de Computadores en el Departamento de Ingeniería y Tecnología de Computadores

#### **AUTORIZAN:**

La presentación de la Tesis Doctoral titulada «Efficient and Scalable Cache Coherence for Many-Core Chip Multiprocessors», realizada por D. Alberto Ros Bardisa, bajo su inmediata dirección y supervisión, y que presenta para la obtención del grado de Doctor por la Universidad de Murcia.

En Murcia, a 26 de Junio de 2009.

Fdo: Dr. José Manuel García Carrasco

Fdo: Dr. Manuel Eugenio Acacio Sánchez

| D. Antonio Javier Cuenca Muñoz, Profesor Titular de Universidad del Área    |

|-----------------------------------------------------------------------------|

| de Arquitectura y Tecnología de Computadores y Director del Departamento de |

| Ingeniería y Tecnología de Computadores, INFORMA:                           |

Que la Tesis Doctoral titulada «Efficient and Scalable Cache Coherence for Many-Core Chip Multiprocessors», ha sido realizada por D. Alberto Ros Bardisa, bajo la inmediata dirección y supervisión de D. José Manuel García Carrasco y de D. Manuel Eugenio Acacio Sánchez, y que el Departamento ha dado su conformidad para que sea presentada ante la Comisión de Doctorado.

En Murcia, a 26 de Junio de 2009.

Fdo: Dr. Antonio Javier Cuenca Muñoz

## **Abstract**

The huge number of transistors that are currently offered in a single die has made major microprocessor vendors shift towards multi-core architectures in which several processor cores are integrated on a single chip. Although most current chip multiprocessors (CMPs) have a relatively small number of cores (2 to 8), in the near future chips with tens of cores, also known as many-core CMPs, will become more popular.

Since most many-core CMPs are expected to use the hardware-managed coherent caches model for the on-chip memory, the cache coherence protocol will be a key component for achieving good performance in these architectures. Nowadays, directory-based protocols constitute the best alternative to keep cache coherence in large-scale systems. Nevertheless, directory-based protocols have two important issues that prevent them from achieving better scalability: the directory memory overhead and the long cache miss latencies.

The memory overhead of a directory protocol mainly comes from the structures required to keep the coherence (or directory) information. Depending on how this information is organized, its memory overhead could be prohibitive for many-core CMPs. The long L2 miss latencies are a consequence of the access to the directory information (the indirection problem), and its distributed nature. The access to the directory information is necessary before performing coherence actions in directory-based protocols. On the other hand, since both data and directory caches are commonly distributed across the chip (non-uniform cache architecture or NUCA), and wire delays of many-core CMPs will cause cross-chip communications of the order of tens of cycles, the access latency to these structures will be dominated by the wire delay to reach each particular cache bank rather than the time spent accessing the bank itself.

Our efforts in this thesis have focused on these key issues. First, we present a scalable distributed directory organization that copes with the memory overhead of

directory-based protocols. In this directory organization, the memory required to keep all the necessary coherence information does not increase with the number of cores, up to a certain number, which corresponds with the number of sets of the private caches. In this way, our organization requires less area than a traditional directory to keep the same information and, therefore, similar performance is obtained. Besides, this organization allows the implementation of an *implicit replacements* mechanism which is able to remove coherence messages caused by replacements. Hence, this mechanism reduces the total network traffic generated by the coherence protocol which finally translates into savings in terms of power consumption.

Second, we propose a new family of cache coherence protocols called *direct coherence protocols*. These protocols are aimed at avoiding the indirection problem of traditional directory-based protocols, but without relying on broadcasting requests. The key property of these protocols is the assignment of the task of keeping cache coherence to the cache that provides the data block in a cache miss, instead of to the home cache, as happens in directory-based protocols. Indirection is avoided by directly sending requests to that cache. This indirection avoidance reduces the average cache miss latency and, consequently, the applications' execution time. Since requests are only sent to just one destination, the network traffic is kept low. Additionally, we also analyze the use of compressed sharing codes to reduce the memory overhead in direct coherence protocols.

Finally, we develop a novel mapping policy managed by the OS that reduces the long access latency to a NUCA cache. We name this policy as *distance-aware round-robin* and it tries to map memory pages to the local NUCA bank of the first core that requests a block belonging to that page. In this way, the average access latency to a NUCA cache is reduced. Furthermore, the proposed policy also introduces an upper bound on the deviation of the distribution of memory pages among cache banks, which lessens the number of off-chip accesses. In this way, we reduce the average cache access latency and the number of off-chip accesses, which translates into improvements in applications' execution time.

## Agradecimientos

Mucho ha sido el esfuerzo y dedicación que he empleado para realizar esta tesis, especialmente durante el último año, y como consecuencia, muchas han sido las personas a las que he prestado menos atención de la debida durante este tiempo. Es por ello que a la vez de disculparme, quiero agradecerles la paciencia y comprensión que han tenido conmigo todos estos años.

Las primeras palabras de agradecimiento van dirigidas a mis padres. La educación, valores y ánimos que he recibido de ellos constantemente me han ayudado a cumplir los objetivos que me he ido proponiendo. Han pasado ya diez años desde que decidí estudiar Ingeniería Informática. Entonces también tenía en mente otras carreras, pero fueron ellos los que me animaron a tomar esta decisión de la cual no me arrepiento en absoluto. Mi hermana ha sido también un apoyo muy importante y todo un ejemplo de constancia. A ella también va dedicada esta tesis con especial cariño. Y cómo no, quiero agradecer también el apoyo recibido de mi cuñado Javi, mis tíos, mis primos y demás familiares, que me han ayudado a alcanzar una meta que hace meses veía casi imposible.

Mis amigos de Cartagena han sido un pilar fundamental para mi todos estos años y me han ayudado a despejarme en los momentos de más estrés. Mención especial se merecen Diego, Esteban y Juan Antonio, con los que he compartido muy buenos momentos. A ellos y los demás amigos que me han estado a mi lado todos estos años, muchas gracias.

Hace siete años me vine a vivir a Murcia. Muchos han sido los pisos por los que he pasado y otros tantos los compañeros que he tenido. Ellos han hecho más agradable mi estancia, especialmente Jose, Francisco y Antonio. Jose, compañero de carrera, piso, doctorado, y un gran amigo, ha estado siempre ahí, y ha sido un apoyo muy importante sobre todo en los momentos más difíciles.

También quiero transmitir mis agradecimientos a Elena, a sus padres, Lola y José Alberto, y a toda su familia, a la que tengo un gran aprecio, y que ha

conseguido que desde el primer día me sintiera en Murcia como en mi propia casa. Tampoco puedo olvidar el apoyo recibido de Rosa, Juan y su hijo Alex que me han tratado siempre como uno más de la familia.

Pero sin lugar a dudas, el sitio donde más tiempo he pasado estos años es la universidad y el apoyo recibido de mis amigos y compañeros del departamento ha sido crucial para hacer estos largos días más amenos. La ayuda de Ricardo durante los años de doctorado, e incluso antes, ha sido vital y me ha ahorrado muchos quebraderos de cabeza. La de Rubén, con el inglés y sus consejos, también ha sido esencial. Ellos dos y el resto de compañeros del laboratorio 3.01, Dani, Juan Manuel, Chema y Kenneth, han sido de mucha ayuda manteniendo el cluster siempre operativo, resolviendo mis dudas y compartiendo los descansos en la sala *pachá*. Asímismo, quiero agradecerle a Miguel Ángel M. su colaboración en la creación de las aplicaciones utilizadas en la tesis. Jose, Antonio y Manolo constituyen también una pieza fundamental en mi día a día. Por último, las vueltas al campus con Miguel Ángel N. y los partidos de baloncesto me han ayudado a desconectar después de un largo día de trabajo. A todos vosotros, muchas gracias.

Mi estancia en Edimburgo el verano pasado supuso un cambio importante en mi vida, tanto en lo profesional como en lo personal. Me alegro mucho de haber estado allí esos cuatro meses y de haber conocido a gente tan especial. Thanks to the people working at the Informatics Forum, and especially to Marcelo for giving me chance of joining his research group, and providing very important technical advice. Chronis has been a great colleague and a better friend during my stay, and without him my days in Edinburgh would certainly not have been so enriching. He, Damon, George, Horacio, and the friends who came to my goodbye dinner have been like a family for me those four months. Thanks to everyone.

Finalmente, quiero agredecer a mis directores, José Manuel y Manolo, el apoyo prestado y la confianza depositada en mí todos estos años. Gracias por darme la oportunidad de realizar la tesis en este departamento y en este campo que tanto me gusta.

## **Contents**

| A  | bstra | ct      |                            | 11 |

|----|-------|---------|----------------------------|----|

| A  | grade | cimien  | tos                        | 13 |

| C  | onten | its     |                            | 15 |

| Li | st of | Figures | S                          | 21 |

| Li | st of | Tables  |                            | 25 |

| Li | st of | Acrony  | /ms                        | 27 |

| 0  | Res   | umen    |                            | 31 |

|    | 0.1   | Introd  | lucción                    | 31 |

|    |       | 0.1.1   | Contribuciones de la tesis | 33 |

|    | 0.2   | Entori  | no de evaluación           | 34 |

|    | 0.3   |         |                            | 37 |

|    |       | 0.3.1   |                            | 38 |

|    |       | 0.3.2   |                            | 40 |

|    |       | 0.3.3   |                            | 41 |

|    | 0.4   | Protoc  |                            | 44 |

|    |       | 0.4.1   |                            | 45 |

|    |       | 0.4.2   |                            | 49 |

|    |       | 0.4.3   |                            | 50 |

#### Contents

|   | 0.5  | Política de mapeo de caches sensible a la distancia y a la tasa de |    |  |  |  |  |

|---|------|--------------------------------------------------------------------|----|--|--|--|--|

|   |      | fallos                                                             | 54 |  |  |  |  |

|   |      | 0.5.1 Mapeo sensible a la distancia y a la tasa de fallos          | 55 |  |  |  |  |

|   |      | 0.5.2 Cambio en los bits de indexación de las caches               | 57 |  |  |  |  |

|   |      | 0.5.3 Resultados                                                   | 58 |  |  |  |  |

|   | 0.6  | Conclusiones y vías futuras                                        | 61 |  |  |  |  |

| 1 | Intr | oduction and Motivation                                            | 63 |  |  |  |  |

|   | 1.1  | The cache coherence problem                                        | 65 |  |  |  |  |

|   | 1.2  | Cache hierarchy organization                                       | 68 |  |  |  |  |

|   | 1.3  | Thesis contributions                                               | 69 |  |  |  |  |

|   | 1.4  | Thesis overview                                                    | 71 |  |  |  |  |

| 2 | Bacl | kground                                                            | 73 |  |  |  |  |

|   | 2.1  | Private versus shared organization                                 | 74 |  |  |  |  |

|   | 2.2  | Cache coherence protocols                                          | 76 |  |  |  |  |

|   | 2.3  | Design space for cache coherence protocols                         | 77 |  |  |  |  |

|   |      | 2.3.1 Optimization for migratory sharing                           | 82 |  |  |  |  |

|   | 2.4  | Protocols for unordered networks                                   | 82 |  |  |  |  |

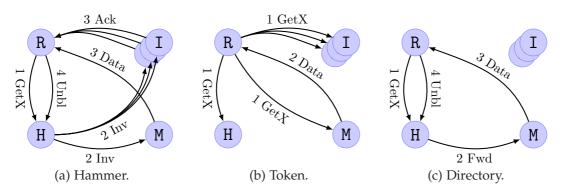

|   |      | 2.4.1 Hammer protocol                                              | 83 |  |  |  |  |

|   |      | 2.4.2 Token protocol                                               | 84 |  |  |  |  |

|   |      | 2.4.3 Directory protocol                                           | 85 |  |  |  |  |

|   |      | 2.4.4 Summary                                                      | 87 |  |  |  |  |

|   | 2.5  | Sending unblock messages                                           | 88 |  |  |  |  |

| 3 | Eval | luation Methodology                                                | 91 |  |  |  |  |

|   | 3.1  | Simulation tools                                                   | 92 |  |  |  |  |

|   |      | 3.1.1 Simics-GEMS                                                  | 92 |  |  |  |  |

|   |      | 3.1.2 SiCoSys                                                      | 93 |  |  |  |  |

|   |      | 3.1.3 CACTI                                                        | 94 |  |  |  |  |

|   | 3.2  | Simulated system                                                   | 94 |  |  |  |  |

|   | 3.3  | Metrics and methods                                                | 96 |  |  |  |  |

|   | 3 4  | Benchmarks                                                         | 98 |  |  |  |  |

|   |      | 3.4.1   | Scientific workloads                                   | . 99  |

|---|------|---------|--------------------------------------------------------|-------|

|   |      | 3.4.2   | Multimedia workloads                                   | . 102 |

|   |      | 3.4.3   | Multi-programmed workloads                             | . 103 |

| 4 | A S  | calable | Organization for Distributed Directories               | 105   |

|   | 4.1  | Introd  | duction                                                | . 105 |

|   | 4.2  | Backg   | round on directory organizations                       | . 107 |

|   |      | 4.2.1   | Directory organizations for CMPs                       | . 111 |

|   | 4.3  | Scalal  | ole directory organization                             | . 113 |

|   |      | 4.3.1   | Granularity of directory interleaving                  | . 113 |

|   |      | 4.3.2   | Conditions required for ensuring directory scalability | . 115 |

|   |      | 4.3.3   | Directory structure                                    | . 117 |

|   |      | 4.3.4   | Changes in the cache coherence protocol                | . 118 |

|   | 4.4  | Impli   | cit replacements                                       | . 119 |

|   | 4.5  | Evalu   | ation results and analysis                             | . 121 |

|   |      | 4.5.1   | Directory memory overhead                              | . 121 |

|   |      | 4.5.2   | Reductions in number of coherence messages             | . 123 |

|   |      | 4.5.3   | Impact on execution time                               | . 125 |

|   | 4.6  | Mana    | ging scalability limits and locality issues            | . 126 |

|   |      | 4.6.1   | Scalability limits                                     | . 126 |

|   |      | 4.6.2   | Locality of the accesses to the shared cache           | . 128 |

|   | 4.7  | Concl   | usions                                                 | . 129 |

| 5 | Dire | ect Col | nerence Protocols                                      | 131   |

|   | 5.1  | Introd  | luction                                                | . 131 |

|   | 5.2  | Relate  | ed work and background                                 | . 134 |

|   |      | 5.2.1   | The lightweight directory architecture                 | . 136 |

|   | 5.3  | Direc   | t coherence protocols                                  |       |

|   |      | 5.3.1   | Direct coherence basis                                 |       |

|   |      | 5.3.2   | Changes to the structure of the tiles of a CMP         |       |

|   |      | 5.3.3   | Description of the cache coherence protocol            |       |

|   |      | 5.3.4   | Preventing starvation                                  |       |

|   | 5.4  | Upda    | ting the L1 coherence cache                            |       |

## Contents

|   | 5.5  | Area    | and power considerations                                  | 152 |

|---|------|---------|-----------------------------------------------------------|-----|

|   | 5.6  |         | ation results and analysis                                |     |

|   |      | 5.6.1   | Impact on the number of hops needed to solve cache misses |     |

|   |      | 5.6.2   | Impact on cache miss latencies                            |     |

|   |      | 5.6.3   | Impact on network traffic                                 |     |

|   |      | 5.6.4   | Impact on execution time                                  |     |

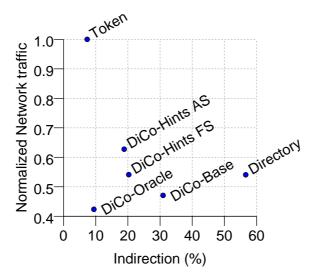

|   |      | 5.6.5   | Trade-off between network traffic and indirection         |     |

|   | 5.7  |         | usions                                                    |     |

| 6 | Traf | fic-Are | a Trade-Off in Direct Coherence Protocols                 | 167 |

|   | 6.1  | Introd  | luction                                                   | 167 |

|   | 6.2  |         | fication of cache coherence protocols                     |     |

|   |      | 6.2.1   | Traditional protocols                                     |     |

|   |      | 6.2.2   | Indirection-aware protocols                               |     |

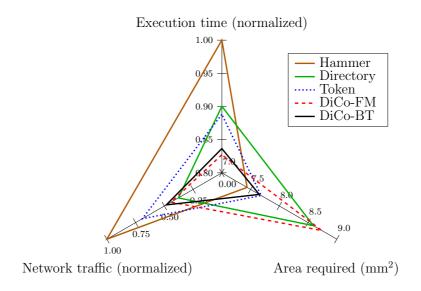

|   |      | 6.2.3   | Summary                                                   |     |

|   | 6.3  | Redu    | cing memory overhead                                      |     |

|   | 6.4  | Evalu   | ation results and analysis                                | 174 |

|   |      | 6.4.1   | Impact on area overhead                                   |     |

|   |      | 6.4.2   | Impact on network traffic                                 |     |

|   |      | 6.4.3   | Trade-off between network traffic and area requirements   |     |

|   |      | 6.4.4   | Impact on execution time                                  |     |

|   |      | 6.4.5   | Overall analysis                                          |     |

|   | 6.5  | Concl   | usions                                                    | 180 |

| 7 | A D  | istance | e-Aware Mapping Policy for NUCA Caches                    | 183 |

|   | 7.1  | Introd  | luction                                                   | 183 |

|   | 7.2  | Backg   | round and related work                                    | 186 |

|   |      | 7.2.1   | Background on mapping policies in NUCA caches             | 186 |

|   |      | 7.2.2   | Related work                                              | 188 |

|   | 7.3  | Distar  | nce-aware round-robin mapping                             | 190 |

|   | 7.4  |         | ouch mapping and private cache indexing                   |     |

|   | 7.5  |         | ation results and analysis                                |     |

|   |      | 7.5.1   | Private cache indexing and miss rate                      | 195 |

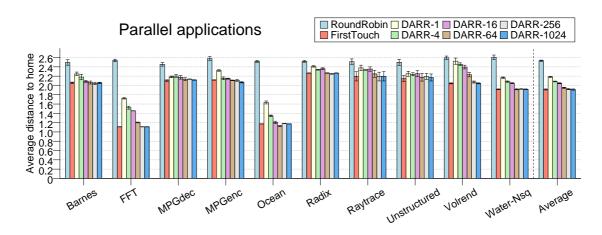

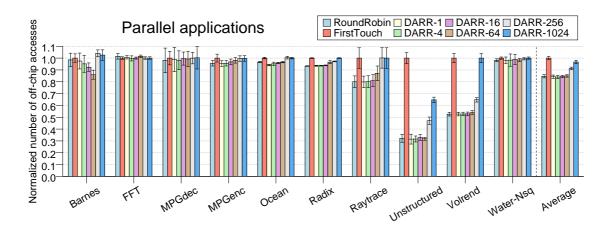

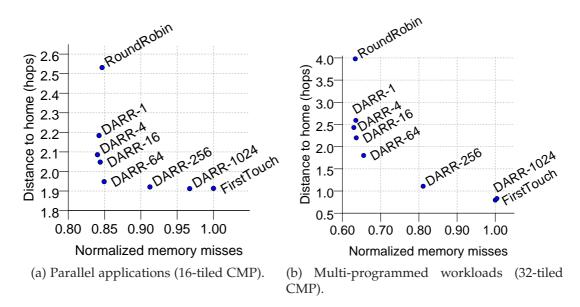

|     |                  | 7.5.2   | Average distance to the home banks                         | 198 |  |  |  |

|-----|------------------|---------|------------------------------------------------------------|-----|--|--|--|

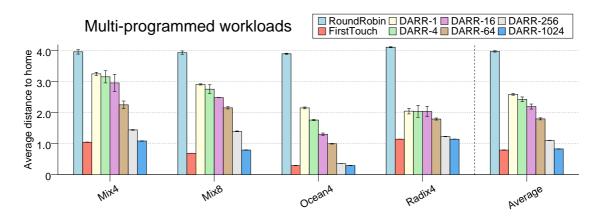

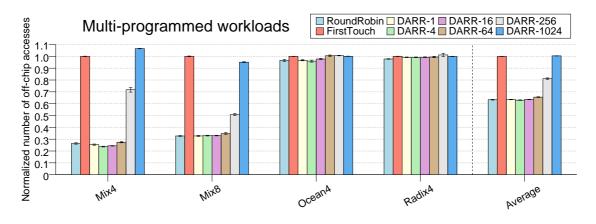

|     |                  | 7.5.3   | Number of off-chip accesses                                | 199 |  |  |  |

|     |                  | 7.5.4   | Trade-off between distance to home and off-chip accesses . | 201 |  |  |  |

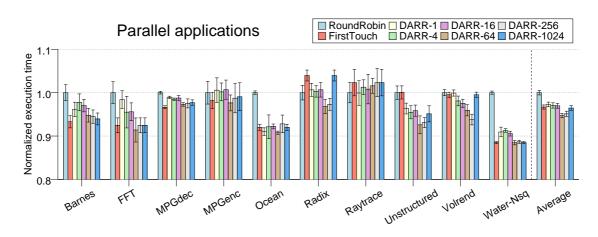

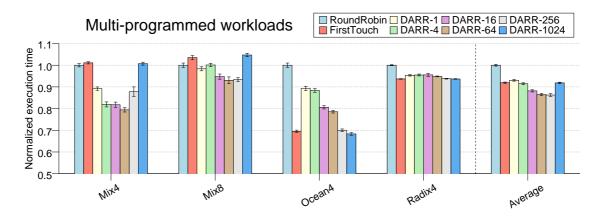

|     |                  | 7.5.5   | Execution time                                             | 202 |  |  |  |

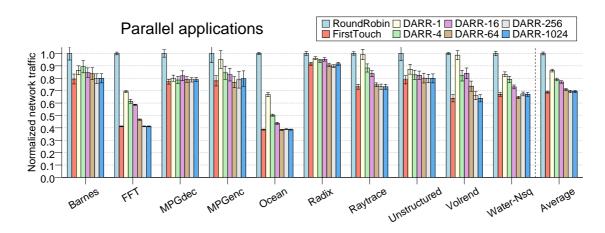

|     |                  | 7.5.6   | Network traffic                                            | 202 |  |  |  |

|     | 7.6              | Concl   | usions                                                     | 205 |  |  |  |

| 8   | Con              | clusior | ns and Future Directions                                   | 207 |  |  |  |

|     | 8.1              | Concl   | usions                                                     | 207 |  |  |  |

|     | 8.2              | Future  | e directions                                               | 213 |  |  |  |

| A   | Dire             | ect Coh | erence Protocol Specification                              | 217 |  |  |  |

| Bil | 3ibliography 225 |         |                                                            |     |  |  |  |

## **List of Figures**

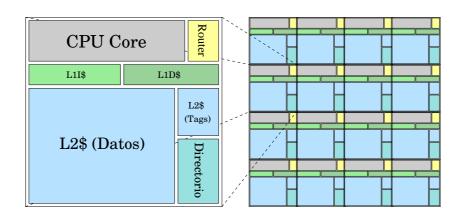

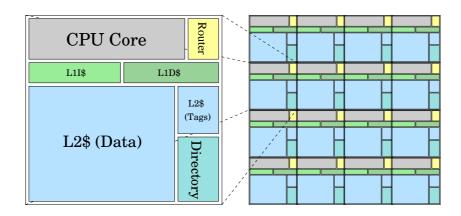

| 0.1  | Organización de un <i>tile</i> y un <i>tiled</i> CMP de $4\times4$ celdas | 35 |

|------|---------------------------------------------------------------------------|----|

| 0.2  | Granularidad del intercalado de directorio y efecto que causa en el       |    |

|      | tamaño mínimo necesario para almacenar toda la información de las         |    |

|      | caches privadas                                                           | 38 |

| 0.3  | Mapeo entre entradas de cache y directorio                                | 39 |

| 0.4  | Diferencias entre los reemplazos tradicionales e implícitos               | 41 |

| 0.5  | Sobrecarga del área de directorio en $mm^2$ en función del número de      |    |

|      | nodos                                                                     | 42 |

| 0.6  | Reducción en el número de mensajes de coherencia                          | 43 |

| 0.7  | Cómo se resuelven los fallos de transferencia de cache a cache en un      |    |

|      | protocolo de directorio y en un protocolo de coherencia directa           | 45 |

| 0.8  | Cómo se resuelven los fallos por actualización (upgrades) en un pro-      |    |

|      | tocolo de directorio y en un protocolo de coherencia directa              | 46 |

| 0.9  | Modificaciones requeridas por los protocolos de coherencia directa        |    |

|      | en la estructura de un <i>tile</i>                                        | 47 |

| 0.10 | Sobrecarga del área de directorio en $mm^2$ en función del número de      |    |

|      | nodos                                                                     | 51 |

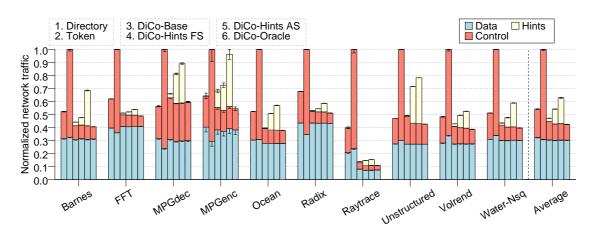

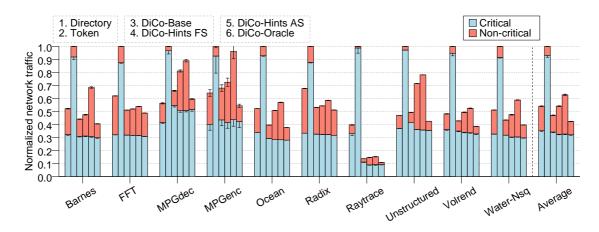

| 0.11 | Tráfico de red normalizado                                                | 52 |

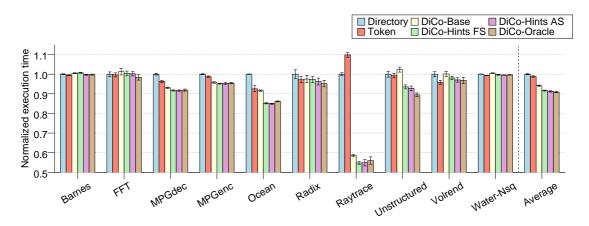

| 0.12 | Tiempo de ejecución normalizado                                           | 53 |

| 0.13 | Ejemplo de la política de mapeo propuesta                                 | 56 |

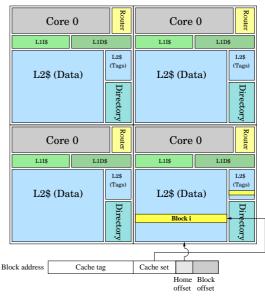

| 0.14 | Cambios en los bits de indexación de las caches                           | 57 |

| 0.15 | Tiempo de ejecución normalizado                                           | 59 |

### LIST OF FIGURES

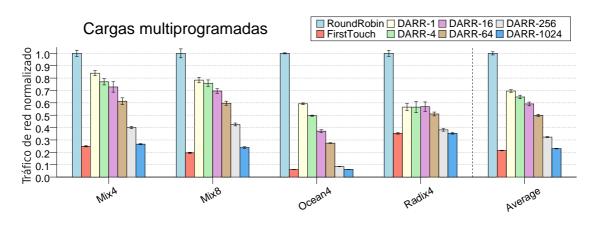

| 0.16 | Tráfico de red normalizado                                             | 60  |

|------|------------------------------------------------------------------------|-----|

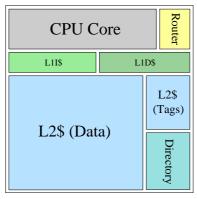

| 1.1  | Organization of a tile and a $4\times4$ tiled CMP                      | 65  |

| 2.1  | Private and shared L2 cache organizations                              | 75  |

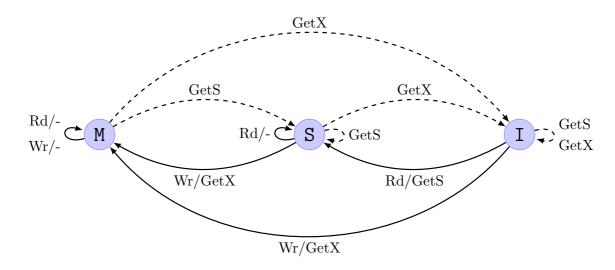

| 2.2  | State transition diagram for a MSI protocol                            | 79  |

| 2.3  | State transition diagram for a MESI protocol                           | 80  |

| 2.4  | State transition diagram for a MOESI protocol                          | 81  |

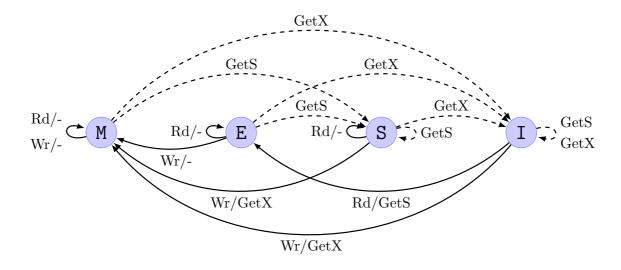

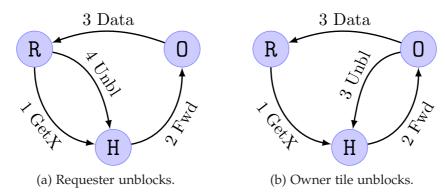

| 2.5  | A cache-to-cache transfer miss in each one of the described protocols. | 84  |

| 2.6  | Management of unblock messages for cache-to-cache transfer misses.     | 88  |

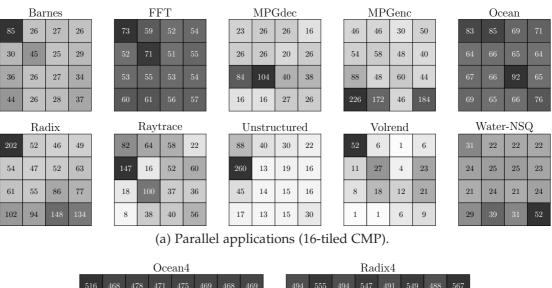

| 3.1  | Multi-programmed workloads evaluated in this thesis                    | 103 |

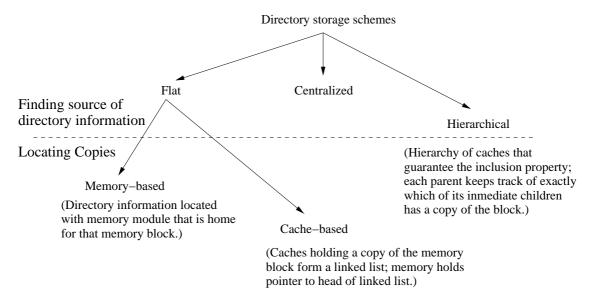

| 4.1  | Alternatives for storing directory information                         | 108 |

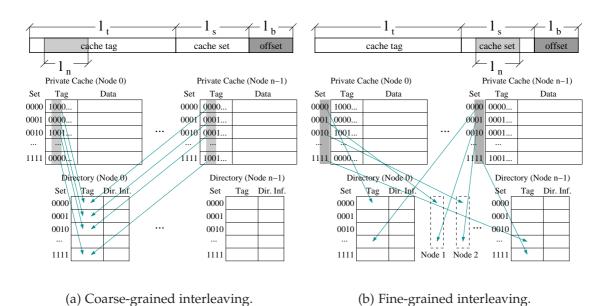

| 4.2  | Granularity of directory interleaving and its effect on directory size | 114 |

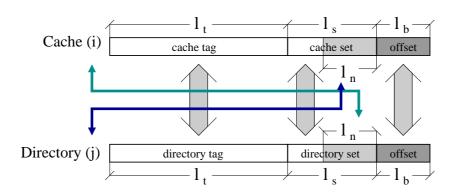

| 4.3  | Mapping between cache entries and directory entries                    | 116 |

| 4.4  | Finding coherence information                                          | 118 |

| 4.5  | Differences between the proposed coherence protocol and a tradi-       |     |

|      | tional coherence protocol                                              | 120 |

| 4.6  | Directory memory overhead as a function of the number of tiles         | 122 |

| 4.7  | Reductions in number of coherence messages                             | 124 |

| 4.8  | Impact on execution time                                               | 126 |

| 4.9  | Directory memory overhead for two different systems and several        |     |

|      | configurations                                                         | 127 |

| 5.1  | Trade-off between <i>Token</i> and directory protocols                 | 132 |

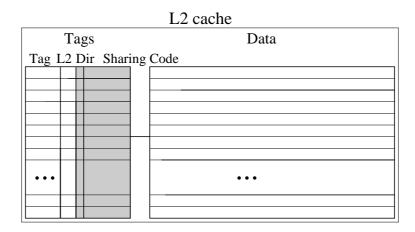

| 5.2  | Cache design for the lightweight directory architecture                | 139 |

| 5.3  | How cache-to-cache transfer misses are solved in directory and direct  |     |

|      | coherence protocols                                                    | 140 |

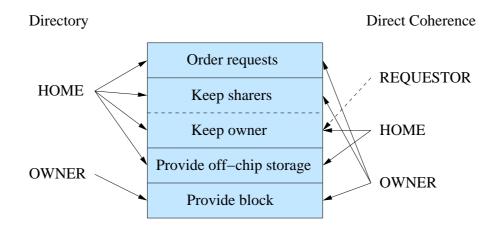

| 5.4  | Tasks performed in cache coherence protocols                           | 141 |

| 5.5  | How upgrades are solved in directory and direct coherence protocols.   | 142 |

| 5.6  | Modifications to the structure of a tile required by direct coherence  |     |

|      | protocols                                                              | 144 |

| 5.7  | Example of ownership change upon write misses                          | 147 |

| 5.8  | Example of a starvation scenario in direct coherence protocols 149       |

|------|--------------------------------------------------------------------------|

| 5.9  | Organization of the address signature mechanism proposed to send         |

|      | hints                                                                    |

| 5.10 | How each miss type is solved                                             |

| 5.11 | Normalized L1 cache miss latency                                         |

| 5.12 | Normalized network traffic                                               |

| 5.13 | Normalized execution time                                                |

| 5.14 | Trade-off between network traffic and indirection                        |

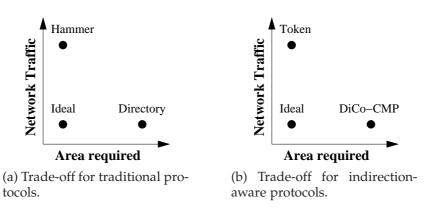

| 6.1  | Traffic-area trade-off in cache coherence protocols                      |

| 6.2  | Overhead introduced by the cache coherence protocols 175                 |

| 6.3  | Normalized network traffic                                               |

| 6.4  | Traffic-area trade-off                                                   |

| 6.5  | Normalized execution time                                                |

| 6.6  | Trade-off among the three main design goals for coherence protocols. 179 |

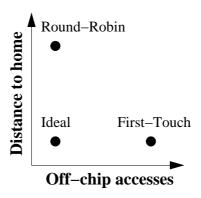

| 7.1  | Trade-off between <i>round-robin</i> and <i>first-touch</i> policies     |

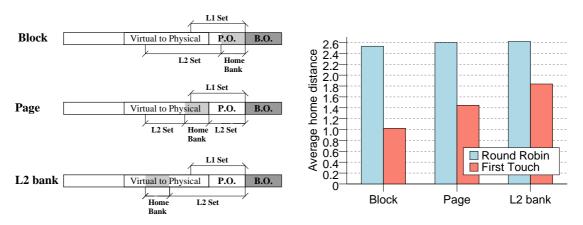

| 7.2  | Granularity of L2 cache interleaving and its impact on average home      |

|      | distance                                                                 |

| 7.3  | Behavior of the distance-aware round-robin mapping policy 191            |

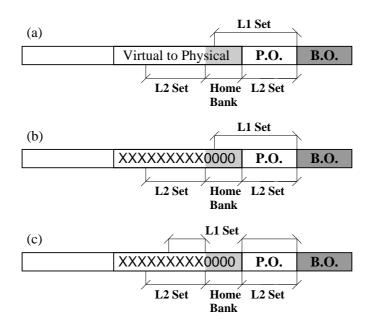

| 7.4  | Changes in the L1 cache indexing policy                                  |

| 7.5  | Number of pages mapped to each cache bank in a first-touch policy 195    |

| 7.6  | Impact of the changes in the indexing of the private L1 caches on        |

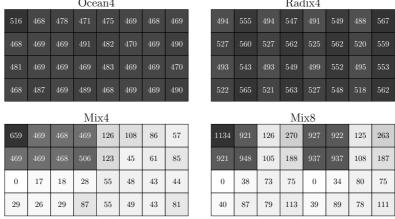

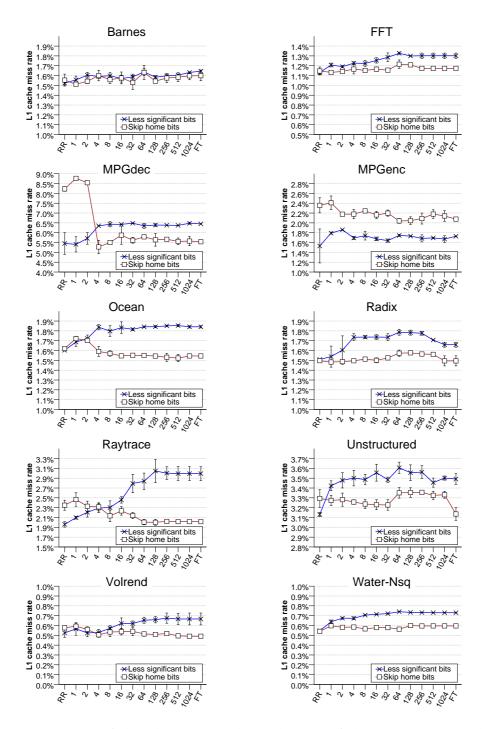

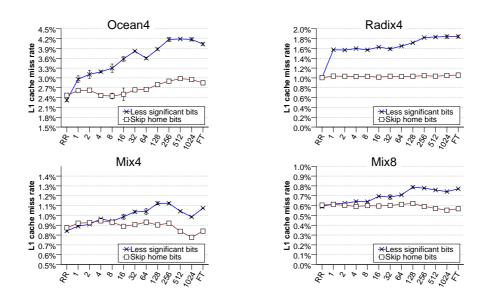

|      | parallel applications                                                    |

| 7.7  | Impact of the changes in the indexing of the private L1 caches on        |

|      | multi-programmed workloads                                               |

| 7.8  | Average distance between requestor and home tile 199                     |

| 7.9  | Normalized number of off-chip accesses                                   |

| 7.10 | Trade-off between distance to home and off-chip accesses 201             |

| 7.11 | Normalized execution time                                                |

| 7.12 | Normalized network traffic                                               |

## **List of Tables**

| 0.1 | Parámetros del sistema simulado                                       |

|-----|-----------------------------------------------------------------------|

| 0.2 | Bits requeridos para almacenar la información de coherencia 49        |

| 0.3 | Resumen de los protocolos evaluados                                   |

| 2.1 | Properties of blocks according to their cache state                   |

| 2.2 | Summary of cache coherence protocols                                  |

| 3.1 | System parameters                                                     |

| 3.2 | Benchmarks and input sizes used in the simulations                    |

| 5.1 | Memory overhead introduced by coherence information (per tile) in     |

|     | a 4x4 tiled CMP                                                       |

| 5.2 | Area overhead introduced by coherence information (per tile) in a 4x4 |

|     | tiled CMP                                                             |

| 6.1 | Summary of cache coherence protocols                                  |

| 6.2 | Bits required for storing coherence information                       |

| A.1 | Coherence messages                                                    |

| A.2 | Processor messages                                                    |

| A.3 | L1 cache controller states                                            |

| A.4 | L1 cache controller events                                            |

| A.5 | L1 cache controller actions                                           |

| A.6 | L1 cache controller transitions                                       |

#### LIST OF TABLES

| A.7 L2 cache controller states       |

|--------------------------------------|

| A.8 L2 cache controller events       |

| A.9 L2 cache controller actions      |

| A.10 L2 cache controller transitions |

| A.11 Memory controller states        |

| A.12 Memory controller events        |

| A.13 Memory controller actions       |

| A.14 Memory controller transitions   |

## **List of Acronyms**

AS: Address Signatures.

**ASR:** Adaptive Selective Replication.

**BT:** Binary Tree.

**CACTI:** Cache Access and Cycle Time Information.

cc-NUMA: cache coherent Non Uniform Memory Access.

**CCR:** Complete and Concise Remote (directory).

**CMP:** Chip MultiProcessor.

CV: Coarse Vector.

**DARR:** Distance-Aware Round-Robin.

**DCT:** Discrete Cosine Transform.

**DiCo:** Direct Coherence.

FFT: Fast Fourier Transform.

FIFO: First In First Out.

**FM:** Full-Map.

**FS:** Frequent Sharers.

FT: First-Touch.

**GEMS:** General Execution-driven Multiprocessor Simulator.

#### LIST OF TABLES

HTML: HyperText Markup Language.

**IDCT:** Inverse Discrete Cosine Transform.

**IEEE:** Institute of Electrical and Electronics Engineers.

ILP: Instruction Level Parallelism.

**INSO:** In-Network Snoop Ordering.

**IPC:** Instructions Per Cycle.

L1C\$: First-Level Coherence Cache.

**L2C**\$: Second-Level Coherence Cache.

LP: Limited Pointers.

LRU: Least Recently Used.

MESI: Modified Exclusive Shared Invalid (set of cache coherence states).

**MOESI:** Modified Owned Exclusive Shared Invalid (set of cache coherence states).

MOSI: Modified Owned Shared Invalid (set of cache coherence states).

**MPEG:** Moving Picture Experts Group.

MSHR: Miss Status Holding Register.

MSI: Modified Shared Invalid (set of cache coherence states).

**MSSG:** MPEG Software Simulation Group.

**NoSC:** No Sharing Code.

**NUCA:** Non Uniform Cache Architecture.

**NUMA:** Non Uniform Memory Access.

**OLTP:** OnLine Transaction Processing.

**OS:** Operating System.

RR: Round-Robin.

**SCI:** Scalable Coherent Interface.

SGI: Silicon Graphics, Inc..

**SGML:** Standard Generalized Markup Language.

SiCoSys: Simulator of Communication Systems.

**SLICC:** Specification Language for Implementing Cache Coherence.

TLB: Translation Lookaside Buffer.

TLP: Thread Level Parallelism.

**VLC:** Variable Length Coding.

VLSI: Very Large Scale of Integration.

VM: Victim Migration.

VR: Victim Replication.

**VTC:** Virtual Tree Coherence.

## Chapter 0

## Resumen

#### 0.1 Introducción

Los continuos avances en la escala de integración permiten reducir cada vez más el tamaño de los transistores y, por tanto, cada vez podemos encontrar chips con un mayor número de transistores disponibles. Los fabricantes de chips han decidido dedicar estos transistores a aumentar el número de procesadores en lugar de a incrementar el rendimiento de un único procesador, tarea mucho más laboriosa y con menores beneficios en términos de rendimiento, dando lugar a los multiprocesadores en un único chip o CMPs (*Chip-multiprocessors*) [91]. Los CMPs tienen importantes ventajas sobre los procesadores superescalares. Por ejemplo, tienen un poder computacional agregado mucho mayor y consumen menos energía que un único procesador mucho más complejo.

Muchos CMPs actuales, como el IBM Power6 [63] o el Sun UltraSPARC T2 [105], tienen un número de procesadores relativamente pequeño (entre 2 y 8), cada uno de ellos con al menos un nivel de caches privadas. Estos procesadores se comunican entre sí a través de una red de interconexión ordenada (habitualmente, un bus o un *crossbar*) que se encuentra dentro del chip. Sin embargo, estas redes de interconexión ordenadas tienen problemas de escalabilidad cuando el número de procesadores que tienen que soportar es relativamente alto. Estos problemas se deben principalmente al área que necesitan para ser implementadas y a su elevado consumo de energía [59]. Además, según la Ley de Moore [83], todavía válida, cabe esperar que el número de procesadores integrados en un mismo chip se doble cada 18 meses [22], por lo que estas redes de interco-

nexión no serán adecuadas para futuros CMPs. Para solucionar estos problemas de escalabilidad surgen los *tiled CMPs*, CMPs que se construyen en base a replicar bloques idénticos o casi idénticos a lo largo y ancho del chip, conectándolos mediante una red de interconexión escalable y punto a punto. Estos bloques de construcción poseen su propio procesador, jerarquía de memoria e interfaz de red. De este modo, se consigue un coste de fabricación menor, ya que su diseño, más sencillo, consiste en replicar un mismo patrón sucesivas veces.

Por otro lado, la mayoría de los CMPs actuales siguen un modelo de programación de memoria compartida. Este modelo proporciona una programación más amigable para el usuario que el modelo de paso de mensajes, pero requiere un soporte eficiente para la coherencia de las caches. Aunque en las últimas décadas se le ha prestado mucha atención a los protocolos de coherencia de caches en el ámbito de los multiprocesadores tradicionales, los parámetros tecnológicos y nuevas restricciones de los CMPs implican la necesidad de buscar nuevas soluciones al problema de la coherencia de caches [22].

Los multiprocesadores que emplean redes de interconexión punto a punto, como los *tiled CMPs*, suelen implementar un protocolo de coherencia de caches basado en directorio. Desafortunadamente, estos protocolos tienen dos problemas fundamentales que limitan su escalabilidad: La alta latencia de los fallos de cache debido a la indirección al nodo *home* y la elevada sobrecarga de memoria necesaria para mantener la información de coherencia.

- La indirección se produce por la necesidad de obtener la información de directorio antes de realizar las acciones de coherencia correspondientes. Esta información se encuentra habitualmente en el nodo *home* de cada bloque. De este modo, ante un fallo de cache se accede, en primer lugar, al nodo *home*. Una vez que se obtiene la información de directorio, se reenvían las peticiones a los destinatarios correspondientes, los cuales responden al nodo que generó el fallo de cache. De este modo, muchos fallos de cache necesitan tres *saltos* en el camino crítico.

- La memoria necesaria para mantener la información de coherencia puede llegar a requerir un área desmesurada cuando el número de nodos del sistema aumenta considerablemente [15]. Esto ocurre especialmente cuando se usa un vector de bits para mantener la información acerca de los compartidores de cada bloque de memoria.

Aunque existen soluciones para mantener la coherencia de las caches que evitan la indirección y tratan de reducir la sobrecarga de memoria, como por ejemplo *Token-CMP* [78], estas soluciones están basadas en difusión total (*broad-cast*), es decir, en inundar la red de interconexión con mensajes de coherencia, lo cual eleva la contención y, lo que es más importante, el consumo de energía de la red, el cual puede llegar a alcanzar en algunos casos el 50% del consumo total del chip [71, 117]. En esta tesis se trata tanto el problema de la indirección como el de la sobrecarga de memoria, pero además, teniendo en cuenta al mismo tiempo, el consumo de la red de interconexión.

Por último, existe otra restricción que puede afectar a la escalabilidad de los futuros CMPs. El retardo que introduce la red de interconexión al enviar un mensaje de un extremo del chip a otro, puede alcanzar las decenas de ciclos [50, 10]. Este retardo provoca que el acceso a una cache lógicamente compartida pero físicamente distribuida dependa en gran medida de la distancia entre el procesador que quiere acceder al dato y el banco de la cache donde esté almacenado dicho dato. Es lo que comúnmente se conoce como caches de acceso no uniforme (NUCA, o *Non-Uniform Cache Architecture* [57]). Por tanto, esta tesis también aborda el problema de la alta latencia de acceso a caches NUCA.

#### 0.1.1 Contribuciones de la tesis

Las principales contribuciones de esta tesis son las siguientes:

- Organización de directorio escalable. Esta organización está basada en duplicar en el directorio los tags de los bloques almacenados en las caches privadas. Además, mediante el uso de un particular intercalado de los bloques de memoria en los diferentes bancos que componen el directorio, se obtiene una organización en la que el tamaño de cada banco de directorio no depende del número de nodos o tiles del sistema. Esta propiedad se cumple siempre y cuando el número de nodos del sistema sea menor o igual al número de conjuntos de las caches privadas.

- Protocolo de directorio con reemplazos implícitos. Este protocolo permite eliminar todo el tráfico generado por los reemplazos de bloques en las caches privadas, lo cual se traduce en una reducción del consumo de la red de interconexión. La idea consiste en solapar los mensajes generados por los reemplazos con los mensajes generados por las peticiones que causan dichos reemplazos. Este mecanismo requiere una organización de directorio similar a la descrita en el punto anterior, particularmente, el mismo intercalado de directorio.

- Protocolos de coherencia directa. Esta familia de protocolos evita el problema de la indirección en los protocolos de directorio, pero sin inundar la red con peticiones, tal y como ocurre en los protocolos basados en broadcast. La principal propiedad de los protocolos de coherencia directa es que tanto el manejo de la información de los compartidores de cada bloque como el mantenimiento de la coherencia de caches, la realiza el nodo propietario, es decir, el nodo que provee el bloque ante un fallo de cache. La indirección se evita enviando las peticiones directamente al nodo propietario, de ahí el nombre de coherencia directa.

- Política de mapeo de caches sensible a la distancia y a la tasa de fallos. Esta política intenta mapear páginas de memoria a los bancos de cache pertenecientes al nodo que más veces accede a dichas páginas, con el fin de reducir la latencia de acceso a los bloques contenidos en dicha página. Adicionalmente, esta política introduce una cota superior para diferenciar entre el número de páginas mapeadas a cada banco, con el objetivo de distribuir uniformemente las páginas entre los bancos de cache, y así reducir la tasa de fallos de dicha cache.

Todas las contribuciones que aparecen en la presente tesis han sido publicadas o están siendo consideradas para su publicación en conferencias internacionales [95, 96, 97, 98, 99, 100, 102], revistas [103] o capítulos de libro [101].

## 0.2 Entorno de evaluación

A la hora de llevar a cabo la evaluación de las propuestas presentadas en esta tesis, hemos decidido hacer uso del simulador GEMS 1.3 [77]. GEMS es un simulador que extiende a Virtutech Simics [72] y modela de forma lo suficientemente detallada el sistema de memoria, así como una amplia gama de protocolos de coherencia de caches. Además, para modelar con más precisión el comportamiento de la red de interconexión hemos reemplazado el simulador de red que proporciona GEMS 1.3 por SiCoSys [94], un simulador de red más detallado, el cual hemos modificado para dar soporte al envío de mensajes *multicast*. Asimismo, hemos hecho uso de la herramienta CACTI [116] con el fin de precisar las latencias de acceso a las caches y de medir el área requerida por dichas estructuras. Para ello, hemos asumido que el tamaño de las direcciones físicas es de 40 bits y que usamos una tecnología de proceso de 45nm.

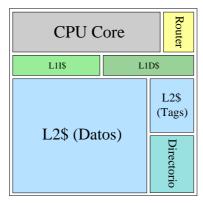

Figura 0.1: Organización de un tile y un tiled CMP de 4×4 celdas.

El sistema simulado en esta tesis es un *tiled* CMP de 16 nodos (o 32, en algunos casos) como el de la Figura 0.1. Cada *tile* contiene un procesador, o *core*, una cache de primer nivel privada para datos y otra para instrucciones, un banco o porción de la cache de segundo nivel compartida y una interfaz de red, o *router*, que conecta todos los nodos mediante una red de interconexión con topología de malla de dos dimensiones. El resto de parámetros del sistema simulado se pueden ver en la Tabla 0.2.

Todas las propuestas presentadas en esta tesis han sido implementadas utilizando para ello el simulador GEMS. Estas propuestas han sido chequeadas exhaustivamente para comprobar la ausencia de condiciones de carrera que pudieran provocar cualquier incoherencia, con el fin de validar su correcto funcionamiento.

Las diez aplicaciones científicas usadas en las simulaciones para evaluar las propuestas presentadas en esta tesis poseen una amplia variedad de patrones de computación y comunicación. Las aplicaciones junto con sus tamaños de entrada son las siguientes. *Barnes* (8192 cuerpos, 4 pasos), *FFT* (64K complejos), *Ocean* (océano de 130x130), *Radix* (512K claves, 1024 de radio), *Raytrace* (teapot), *Volrend* (head) y *Water-NSQ* (512 moléculas, 4 pasos) provienen del conjunto de aplicaciones SPLASH-2 [119]. *Unstructured* (Mesh.2K, 5 pasos) es una aplicación que modela el movimiento de fluidos [86]. *MPGdec* (525\_tens\_040.m2v) y *MPGenc* (salida de *MPGdec*) son aplicaciones multimedia que han sido obtenidas del conjunto de *benchmarks* ALPBench [66].

Aparte de estas aplicaciones paralelas, las cuales simulamos en un CMP con 16 nodos, también hemos simulado cargas multiprogramadas para un CMP con

Tabla 0.1: Parámetros del sistema simulado.

| Parámetros de memoria (GEMS)      |                              |  |  |

|-----------------------------------|------------------------------|--|--|

| Frecuencia del procesador         | 3GHz                         |  |  |

| Jerarquía de cache                | No inclusiva                 |  |  |

| Tamaño de bloque                  | 64 bytes                     |  |  |

| Cache L1 de datos e instrucciones | 128KB, 4 vías                |  |  |

| Tiempo de acceso a la L1          | 1  (tag) + 2  (datos) ciclos |  |  |

| Cache L2 compartida               | 1MB/celda, 8 vías            |  |  |

| Tiempo de acceso a la L2          | 2 (tag) + 4 (datos) ciclos   |  |  |

| Tiempo de acceso al directorio    | 2 ciclos                     |  |  |

| Tiempo de acceso a memoria        | 300 ciclos                   |  |  |

| Tamaño de página                  | 4KB                          |  |  |

| Parámetros de red (SiCoSys)       |                              |  |  |

| Frecuencia de red                 | 1.5GHz                       |  |  |

| Topología                         | Malla de 2 dimensiones       |  |  |

| Técnica de switching              | Wormhole                     |  |  |

| Technique enrutamiento            | X-Y determinista             |  |  |

| Tamaño de los mensajes de control | 1 flit                       |  |  |

| Tamaño de los mensajes de datos   | 4 flits                      |  |  |

| Tiempo de enrutamiento            | 1 ciclo                      |  |  |

| Tiempo de switch                  | 1 ciclo                      |  |  |

| Latencia del enlace (un salto)    | 2 ciclos                     |  |  |

| Ancho de banda del enlace         | 1 flit/ciclo                 |  |  |

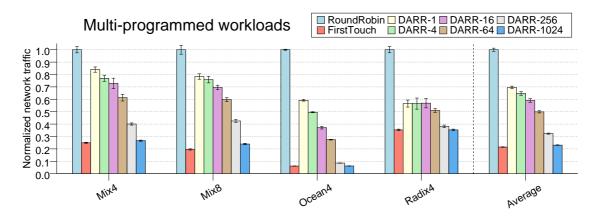

32 nodos. En concreto, hemos creado cuatro cargas multiprogramadas. *Radix4* ejecuta cuatro instancias de *Radix* con 8 hilos cada una. Similarmente, *Ocean4* ejecuta cuatro instancias de *Ocean. Mix4* y *Mix8* simulan instancias de *Ocean, Raytrace, Unstructured* y *Water-Nsq*, con 8 y 4 hilos, respectivamente. *Mix8* ejecuta dos instancias de cada aplicación.

Finalmente, para obtener mayor precisión en los resultados, hemos realizado diversas pruebas para cada configuración y aplicación evaluada, las cuales insertan perturbaciones aleatorias en los accesos a memoria [12]. De este modo, los resultados presentados corresponden a la media de los valores obtenidos. Además, los resultados presentados en esta tesis corresponden a la fase paralela de las aplicaciones.

# 0.3 Una organización de directorio escalable

Como hemos apuntado en la Sección 0.1, los protocolos de coherencia de cache basados en directorio añaden a la implementación final del sistema una sobrecarga de memoria extra. Esta sobrecarga es debida al mantenimiento de la información acerca de los compartidores de cada bloque de memoria, es decir, la información de coherencia o información de directorio. Cuando esta información se organiza como un vector de bits, en el que cada bit indica la presencia o ausencia de un bloque de memoria en una determinada cache, la cantidad de memoria requerida por el directorio aumenta linealmente conforme aumenta el número de nodos. Es por ello por lo que numerosos autores han intentado reducir dicha sobrecarga de memoria a través de códigos de compartición comprimidos [1, 8, 26, 45, 85]. Sin embargo, estos códigos no logran una escalabilidad completa y a menudo introducen mensajes de coherencia extra que repercuten negativamente tanto en el rendimiento como en el consumo de energía del sistema.

En esta tesis proponemos una nueva organización de directorio que lo dota de escalabilidad [99], es decir, mantiene constante la memoria añadida a cada nodo para mantener la información de directorio, hasta un cierto número de procesadores. Además, esta organización almacena información precisa acerca de los compartidores. El tamaño de cada banco de directorio en la organización propuesta es  $c \times (l_t + 2)$ , donde c es el número de entradas de las caches privadas y  $l_t$  es el tamaño de la etiqueta, o tag, almacenado en la cache de directorio. Esta propuesta se detalla en la Sección 0.3.1.

Adicionalmente, partiendo de la organización de directorio diseñada, hemos propuesto un mecanismo de reemplazos implícitos [99]. Este mecanismo, que se describe en la Sección 0.3.2, permite eliminar la totalidad de los mensajes de coherencia causados por los reemplazos en las caches privadas, debido a que estos mensajes se manejan de forma implítita junto con el mensaje de petición que provoca cada reemplazo.

Los resultados, presentados en la Sección 0.3.3, muestran que la sobrecarga de área requerida por la organización de directorio escalable es de tan sólo 0.53% comparado con el área requerida por las caches de datos. Por otro lado, el mecanismo de reemplazos implícitos logra eliminar el 13% de los mensajes generados por un protocolo de directorio cuando los bloques en estado compartido no informan del reemplazo al directorio y es capaz de reducirlos hasta un 33%, de media, cuando se informa al directorio acerca de estos reemplazos.

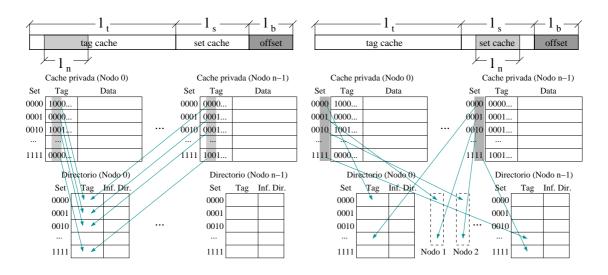

- (a) Intercalado de grano grueso.

- (b) Intercalado de grano fino.

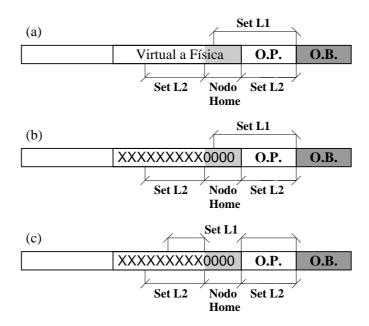

Figura 0.2: Granularidad del intercalado de directorio y efecto que causa en el tamaño mínimo necesario para almacenar toda la información de las caches privadas.

### 0.3.1 Directorio escalable

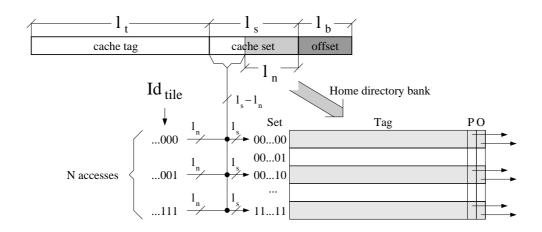

Esta sección describe un protocolo de directorio distribuido en el que cada banco de directorio tiene un tamaño fijo, que es independiente del número de nodos del sistema. Para ello, prestamos especial atención al intercalado del directorio, es decir, a qué banco de directorio mapea cada bloque de memoria. Al nodo donde se encuentra ese banco o cache de directorio se le denomina nodo home de dicho bloque. Normalmente, este mapeo se realiza tomando los  $log_2n$  ( $l_n$ ) bits menos significativos de la dirección del bloque (sin contar con el desplazamiento, u offset, del bloque), donde n representa el número de nodos del sistema. Como muestra la Figura 0.2, dependiendo de la posición de los bits que se elijan para definir el nodo home de cada bloque, el número mínimo de entradas requerido por el directorio puede variar. De hecho, si se toman los bits más significativos de la dirección de memoria, se puede dar el caso de que todos los bloque almacenados en cache mapeen a un mismo home, por lo que se requeriría un número de entradas para el directorio de  $n \times c$ , y por tanto, el tamaño de dicho directorio dependería linealmente del número de nodos.

En cambio, si los bits tomados para asignar el nodo *home* están dentro de los bit usados para indexar las caches privadas  $l_s$ , nos aseguramos de que los

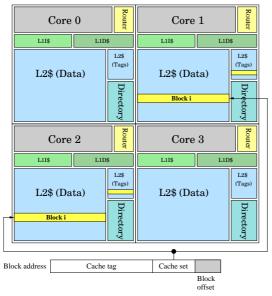

Figura 0.3: Mapeo entre entradas de cache y directorio.

bloques almacenados en las caches se distribuyan uniformemente entre los diferentes nodos *home*. De este modo, el número máximo de entradas requerido por cada banco de directorio sería *c*, valor que no depende del número de nodos, sino tan sólo del número de entradas de las caches privadas.

Por otro lado, para mantener constante su tamaño total necesitamos que, no sólo el número, sino también el tamaño de las entradas, sea independiente del número de nodos. Esto se consigue mediante el uso de *tags* duplicados, que han sido empleados en CMPs como el Piranha [16] o el Sun UltraSPARC T2 [112]. Estos *tags* duplicados mantienen en el directorio una copia de los *tags* almacenados en las caches privadas.

Una vez acotado el tamaño del directorio debemos buscar una función que mapee bloques a entradas de directorio, de tal forma que se cumplan las siguientes premisas:

- 1. Un bloque de memoria siempre debe tener su *tag* duplicado en el mismo banco de directorio, independientemente de la cache privada donde esté almacenado. Esta premisa asegura encontrar toda la información relativa a un mismo bloque en un único nodo.

- 2. La función debe ser inyectiva, es decir uno a uno. Esta premisa garantiza la escalabilidad en el número de entradas del directorio.

La Figura 0.3 muestra esta función. Los nodos *home* vienen definidos por un subconjunto de bits  $l_n$  de entre los usados para indicar el conjunto, o *set*, de la cache privada  $l_s$  donde el bloque debe ser almacenado. El conjunto donde se almacenará el *tag* duplicado dentro de ese banco de directorio viene dado por la

unión de los restante bits del campo  $l_s$  y el identificador del nodo que mantiene su copia en la cache privada. Estos últimos bits serán posteriormente usados para identificar los compartidores del bloque. Ya que los  $l_n$  bits deben ser un subconjunto de los  $l_s$  bits ( $l_n \subseteq l_s$ ), este directorio mantiene su escalabilidad siempre y cuando se cumpla la regla:

$num\_nodos \le num\_conjuntos\_en\_caches\_privadas$ .

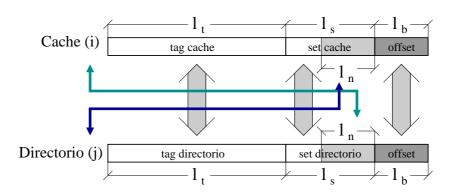

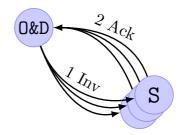

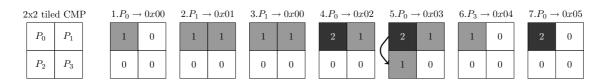

## 0.3.2 Reemplazos implícitos

En esta sección se describe el mecanismo de reemplazos implícitos, que consiste en manejar los reemplazos de forma implícita, uniendo los mensajes generados por ellos con los generados por las peticiones que provocan dichos reemplazos. La organización de directorio presentada anteriormente, asegura que ante el reemplazo de un bloque de una cache privada, se cumplan las dos características descritas a continuación, las cuales permiten implementar el mecanismo de reemplazos implícitos:

- 1. El bloque reemplazado y el bloque que causa su reemplazo siempre mapean al mismo banco de directorio. Esto se debe al intercalado utilizado, que toma los bits para definir el nodo *home* dentro del subconjunto de los bits usados para seleccionar el conjunto donde se almacena el bloque en las caches privadas.

- 2. Cada entrada de las caches privadas tiene asociada una única entrada en el directorio (una única vía también), y viceversa. De este modo cuando la petición que genera el reemplazo llega al directorio, este conoce tanto la dirección del dato solicitado como la del reemplazado. Por tanto, no es necesario indicar ambas direcciones en el mensaje, sino solamente la del bloque solicitado y el número de la vía donde estaba el bloque reemplazado, por lo que el tamaño de los mensajes no se incrementa considerablemente.

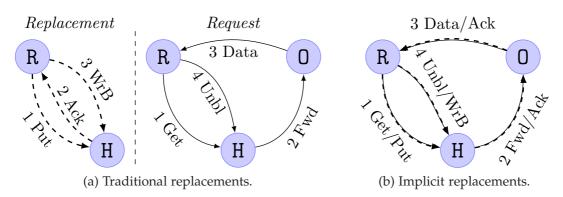

La Figura 0.4 muestra el mecanismo de reemplazos implícitos comparándolo con el mecanismo de reemplazos tradicional. Normalmente, cuando se produce un fallo de cache, previamente se debe reemplazar otro bloque almacenado en el mismo conjunto con el fin de dejar espacio para el nuevo bloque. Los reemplazos se suelen hacer en tres fases para evitar condiciones de carrera difíciles de tratar. Primero, la cache pide permiso de reemplazo al nodo *home* (1 *Put*). Cuando el nodo *home* confirma el reemplazo (2 *Ack*), el bloque es enviado al siguiente nivel

Figura 0.4: Diferencias entre los reemplazos tradicionales e implícitos.

de cache (3 WrB). Por otro lado, las peticiones de bloque que fallan en cache solicitan el bloque al nodo home (1 Get). Esta solicitud es reenviada al nodo propietario (2 Fwd), el cual envía los datos al peticionario (3 Data). Una vez resuelto el fallo, se envía un mensaje (4 Unbl) al nodo home indicándole que ya puede procesar otras peticiones para ese bloque.

Mediante el mecanismo de reemplazos implícitos se solapan estos mensajes, tal y como se muestra en la Figura 0.4b. Ante un fallo, se almacena tanto la dirección del bloque reemplazado como la del solicitado en el MSHR (*Miss Status Hold Register* o registro de fallos pendientes), y se envía la petición (*1 Get/Put*) al nodo *home*. Del mismo modo, el nodo *home* almacena ambas direcciones (la del reemplazo la obtiene del directorio) en su MSHR y reenvía al propietario del bloque solicitado la petición (*2 Fwd/Ack*). Cuando el causante del fallo recibe el mensaje con los datos y la confirmación del reemplazo (*3 Data/Ack*) ambas entradas del MSHR se liberan y se procede al reemplazo del bloque, a la vez que se desbloquea el nodo *home* (*4 Unbl/WrB*). Finalmente, el nodo *home* libera análogamente ambas entradas de su MSHR.

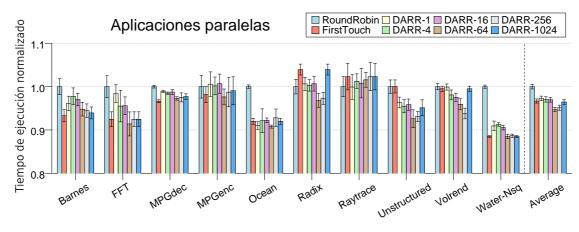

### 0.3.3 Resultados

En esta sección mostramos los resultados obtenidos para las dos propuestas presentadas previamente. En primer lugar veremos como la organización de directorio escalable es capaz de reducir la sobrecarga de memoria del protocolo de coherencia. Después, mostraremos las reducciones en el número de mensajes de coherencia obtenidas por el mecanismo de reemplazos implícitos.

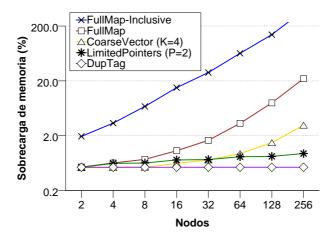

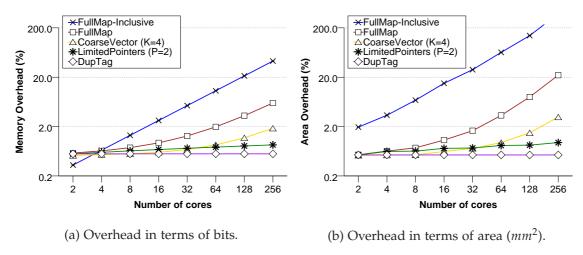

Figura 0.5: Sobrecarga del área de directorio en  $mm^2$  en función del número de nodos.

### 0.3.3.1 Sobrecarga de memoria

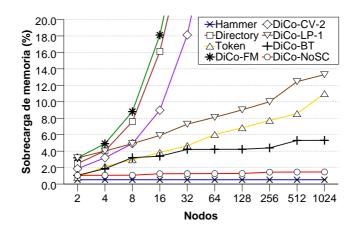

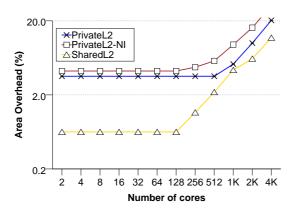

La Figura 0.5 compara diversas organizaciones de directorio. En particular, muestra la sobrecarga que introduce el área requerida por la información de directorio comparada con el área requerida por las caches de datos. Esta sobrecarga se muestra en función del número de nodos del sistema, desde 2 hasta 256 nodos.

Las organizaciones representadas en la gráfica son: *FullMap-Inclusive*, donde la información de directorio está incluida en los *tags* de la cache L2; *FullMap*, que usa una cache de directorio con el mismo número de entradas que la cache L1 y con un vector de bits, o *full-map*, en cada entrada; *CoarseVector* (*K*=4), que usa la cache de directorio anterior comprimiendo el código de compartición usando un bit para representar cuatro nodos [45]; *Limited pointers* (*P*=2), que comprime el código de compartición usando dos punteros para los dos primeros compartidores [26]; y *DupTag*, que es la organización propuesta en esta sección.

Podemos ver que las organizaciones que usan un código de compartición full-map no escalan con el número de nodos del sistema. Las otras propuestas que usan códigos de compartición comprimidos, tampoco escalan completamente, y como veremos en la siguiente sección introducen tráfico extra en la red debido a que almacenan información imprecisa. Por último, nuestra propuesta, no sólo almacena información precisa sino que también escala perfectamente hasta 256 nodos. La sobrecarga de esta organización es de 0.53% para todas las configuraciones mostradas.

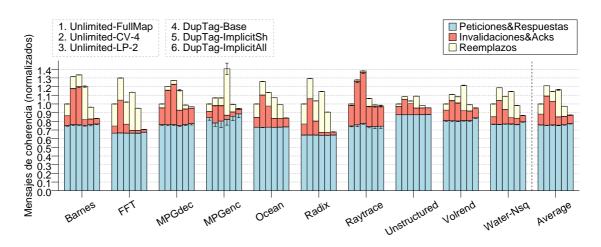

Figura 0.6: Reducción en el número de mensajes de coherencia.

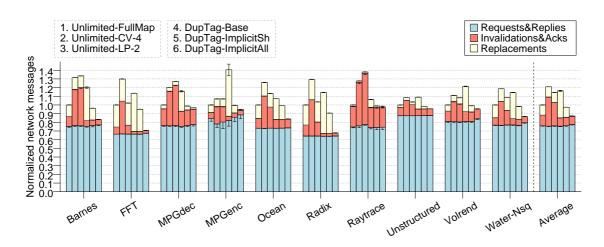

### 0.3.3.2 Tráfico de red

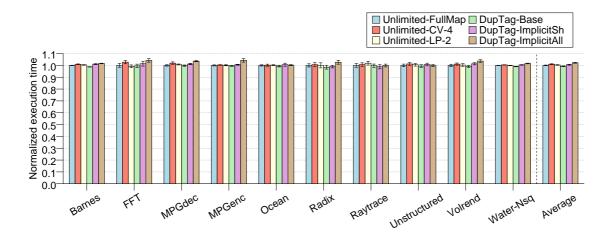

La Figura 0.6 muestra la variación en el número de mensajes generados por el protocolo de coherencia, normalizado respecto a un protocolo de directorio que usa caches de directorio ilimitadas con un código de compartición fullmap (Unlimited-FullMap). Además mostramos resultados para Unlimited-CV-4 y Unlimited-LP-2 que representan protocolos con caches de directorio ilimitadas y con códigos de compartición comprimidos (coarse vector [45] y limited pointers [26], respectivamente). Por último, mostramos resultados para protocolos que usan nuestra organización de directorio escalable, usando reemplazos tradicionales tanto de bloques compartidos como modificados (DupTag-Base), haciendo implícitos los reemplazos compartidos (DupTag-ImplicitSh), y realizando todos los reemplazos de forma implícita (DupTag-ImplicitAll).

En primer lugar podemos observar que el uso de códigos de compartición comprimidos incrementa el tráfico en la red, debido a un aumento en el número de invalidaciones enviadas por cada fallo. Por otro lado, el uso de *tags* duplicados requiere la notificación de reemplazos en estado compartido, lo que incrementa el tráfico debido a los reemplazos. Los reemplazos implícitos eliminan completamente este tráfico, reduciendo así el tráfico de red en un 13% comparado con un protocolo que no informa de los reemplazos de bloques en estado compartido y hasta un 33% cuando sí se informa de estos reemplazos.

## 0.4 Protocolos de coherencia directa

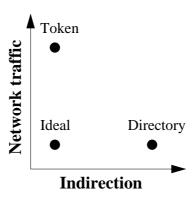

Otro problema importante de los protocolos de directorio es la indirección en el acceso al nodo *home*. El acceso al nodo *home* para obtener la información de directorio causa elevadas latencias en los fallos de cache, degradando el rendimiento final del sistema. Por otro lado, existen otros protocolos que eliminan esta indirección, como por ejemplo *Token-CMP*, pero que a cambio generan una cantidad de tráfico muy importante, especialmente cuando el número de nodos del sistema es elevado.

Esta tesis presenta los protocolos de coherencia directa [97, 98], una nueva familia de protocolos de coherencia de cache que eliminan la indirección para la mayoría de los fallos de cache, tal y como ocurre con *Token-CMP*, pero enviando la petición a un único destinatario, como hacen los protocolos de directorio. En particular, proponemos y evaluamos un protocolo basado en el concepto de coherencia directa para *tiled* CMPs que llamamos *DiCo-CMP*.

Los protocolos de coherencia directa, explicados en la Sección 0.4.1, asignan la tarea de almacenar la información de directorio y de ordenar las peticiones de los diferentes procesadores sobre un mismo bloque de memoria a la cache que provee el bloque en cada fallo. El nodo que contiene esa cache se llama nodo *owner* o propietario. La indirección se evita enviando la petición de fallo de cache directamente al nodo propietario, de ahí el nombre de coherencia directa. De este modo, la coherencia directa reduce la latencia de los fallos de cache respecto a un protocolo de directorio, ya que envía la petición directamente al nodo que debe proveer el dato, a la vez que reduce el tráfico en la red respecto a *Token-CMP*, puesto que la petición es enviada a un único destinatario.

Además, dado que la organización de directorio escalable propuesta en la sección anterior no puede ser utilizada para organizar el código de compartición en los protocolos de coherencia directa, hemos estudiado el uso de diversos códigos comprimidos para estos protocolos (Sección 0.4.2), con el fin de reducir no sólo la indirección y el tráfico en la red, sino también la sobrecarga de memoria requerida por estos protocolos [100].

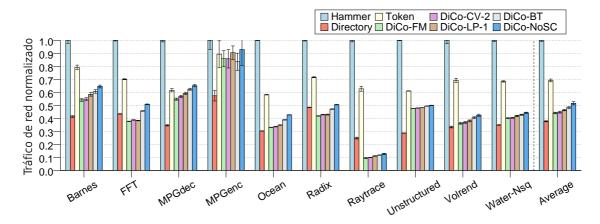

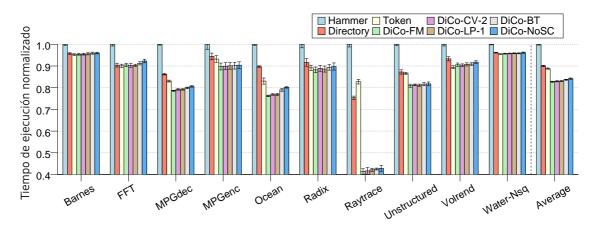

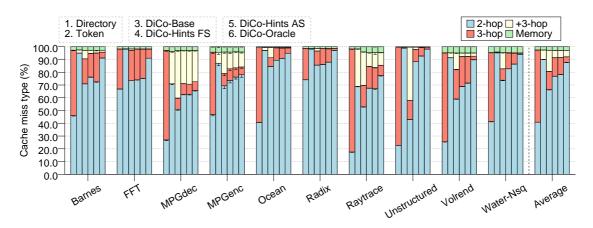

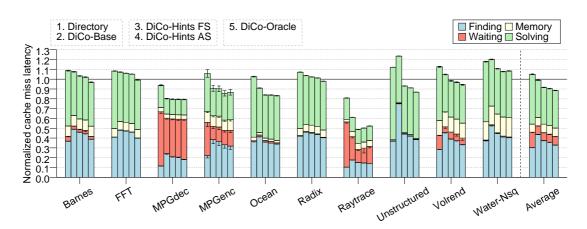

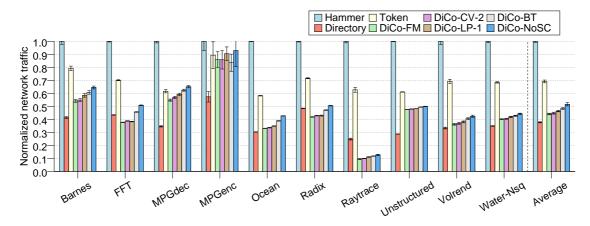

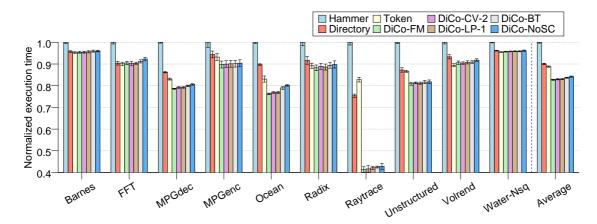

Los resultados, presentados en la Sección 0.4.3, muestran que *DiCo-CMP* reduce el tiempo de ejecución de las aplicaciones en un 9% (media de todas las aplicaciones) comparado con un protocolo de directorio, y un 8% comparado con *Token-CMP*. Además, reduce el tráfico en la red de interconexión, y por tanto el consumo de energía, hasta en un 37% comparado con *Token-CMP*.

Por otro lado, el uso de códigos de compartición comprimidos junto con los protocolos de coherencia directa ofrecen un buen compromiso entre tráfico de

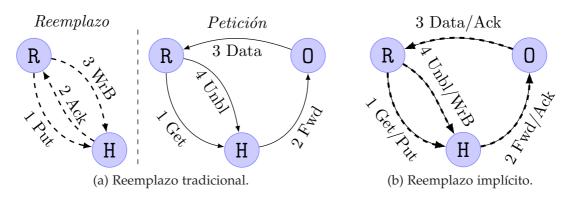

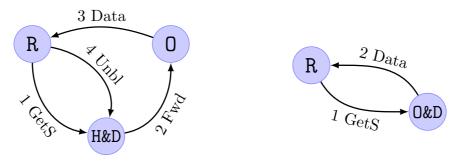

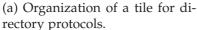

(a) Protocolos de directorio.

(b) Protocolos de coherencia directa.

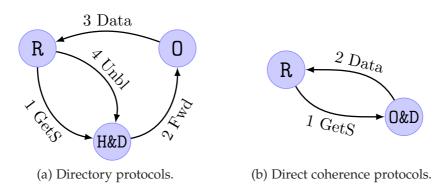

Figura 0.7: Cómo se resuelven los fallos de transferencia de cache a cache en un protocolo de directorio y en un protocolo de coherencia directa. R=Requester o peticionario; H=Home; D=Directorio; O=Owner o propietario.

red y área requerida, sin degradar sustancialmente el tiempo de ejecución. En particular, un código de compartición basado en árboles binarios [1] (DiCo-BT) obtiene importantes reducciones en la sobrecarga de memoria respecto a DiCo-CMP, reduciendo además su orden de crecimiento de O(n) a  $O(log_2n)$ , a cambio de incrementar ligeramente el tráfico en la red en un 9%.

### 0.4.1 La coherencia directa

En los protocolos de directorio, la coherencia de cache es mantenida por el nodo *home* y todos los fallos de cache son enviados a dicho nodo, el cual debe redirigir la petición al nodo propietario. Esto introduce el problema de la indirección, que provoca fallos de cache con mayor latencia. En contrapartida, la coherencia directa almacena la información de coherencia en el nodo propietario de cada bloque y asigna la tarea de mantener la coherencia a dicho nodo. De este modo la indirección se puede evitar si el nodo que comete el fallo envía la petición directamente al propietario del bloque en lugar de al nodo *home*.

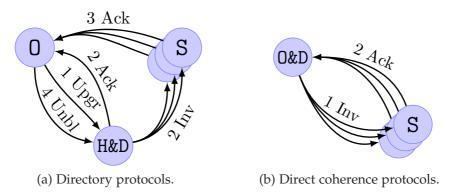

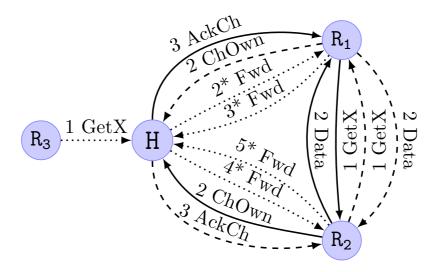

Las figuras 0.7 y 0.8 comparan cómo se resuelven dos tipos distintos de fallos de cache tanto en un protocolo de directorio como en los protocolos de coherencia directa, indicado los números el orden en el que se generan los mensajes. En estas figuras se pueden apreciar las principales ventajas de los protocolos de coherencia directa sobre los protocolos de directorio, que son las siguientes.

• Consiguen que un mayor número de fallos se resuelvan en solamente dos saltos, en lugar de en tres (el mensaje *Unbl*, que aparece en los protocolos

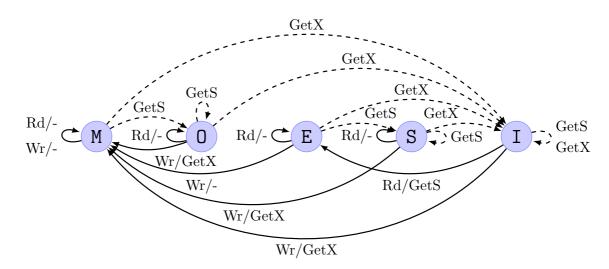

- (a) Protocolos de directorio.

- (b) Protocolos de coherencia directa.

Figura 0.8: Cómo se resuelven los fallos por actualización (*upgrades*) en un protocolo de directorio y en un protocolo de coherencia directa. O=*Owner* o propietario; H=*Home*; D=Directorio; S=*Sharers* o compartidores.

de directorio, se encuentra fuera del camíno crítico del fallo), reduciendo así su latencia.

- Eliminan los mensajes de comunicación entre el nodo propietario y el nodo *home* ya que el mantenimiento de la coherencia de caches y el envío de los datos se realizan ahora en un único nodo.

- Reducen el tiempo de espera de las otras peticiones al mismo bloque, como

consecuencia de eliminar el tiempo que se pierde en la comunicación entre

el nodo propietario y el nodo *home*. Aunque este tiempo se encuentra

fuera del camino crítico del fallo, sí que afecta a los siguientes fallos sobre

el mismo bloque.

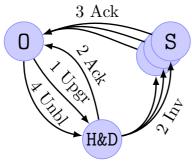

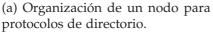

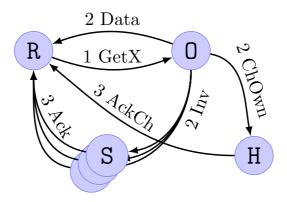

Para implementar los protocolos de coherencia directa se requieren una serie de cambios en la organización de los nodos del sistema. En primer lugar, toda cache que pueda ser propietaria de un bloque debe ser capaz de almacenar el código de compartición de dicho bloque. Por tanto, es necesario ampliar la parte de las etiquetas (*tags*) de las caches de primer nivel con un nuevo campo para almacenar los compartidores (las caches de segundo nivel ya incluyen este campo en un protocolo de directorio). En cambio, la coherencia directa no necesita almacenar esta información en la estructura de directorio del nodo *home*.

Al contrario que en un protocolo de directorio, en la coherencia directa el nodo que mantiene la coherencia no es fijo ya que los fallos de escritura pueden provocar que el nodo propietario cambie. Se necesita, por tanto, un mecanismo para poder identificar al nodo propietario en cualquier momento. Para ello, es

(b) Organización de un nodo para protocolos de coherencia directa.

Figura 0.9: Modificaciones requeridas por los protocolos de coherencia directa en la estructura de un *tile*.

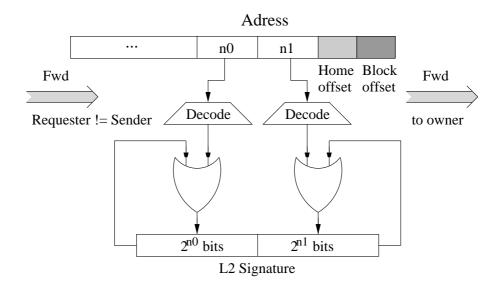

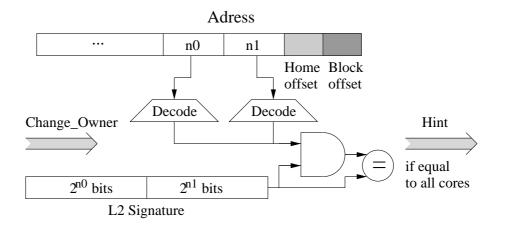

necesario añadir dos estructuras que almacenan información que identifica al nodo propietario ( $log_2n$  bits), como se puede apreciar en la parte derecha de la Figura 0.9:

- Cache de coherencia de primer nivel (L1C\$): Esta cache almacena información sobre los nodos propietarios de un conjunto de bloques y es accedida por el procesador que genera la petición al producirse un fallo de cache. Si la información sobre el propietario del bloque solicitado está almacenada en la cache, se enviará la petición directamente a dicho nodo. Esta cache se puede actualizar de diversas maneras dependiendo del tráfico de red que se desee generar, tal y como se explicará más adelante.

- Cache de coherencia de segundo nivel (L2C\$): Esta cache es necesaria debido a que el nodo encargado de mantener la coherencia puede cambiar durante la ejecución de las aplicaciones. En esta cache se almacena la identidad actual del nodo propietario para todos los bloques almacenados en cualquier cache privada. La información almacenada debe ser actualizada en cada cambio de propietario mediante mensajes de control.

### 0.4.1.1 Evitando la inanición

En los protocolos basados en directorio se consigue evitar la inanición encolando las peticiones en el nodo encargado de ordenarlas (el nodo *home*) y procesán-

dolas en orden FIFO (first in, first out). Sin embargo en los protocolos de coherencia directa el nodo que ordena las peticiones es el nodo propietario, el cual puede cambiar ante una petición de escritura. Debido a esta situación, una petición puede tardar algún tiempo en encontrar el nodo propietario, incluso aunque la petición la envíe el nodo home. Además, una vez encontrado el propietario este puede moverse a otro nodo debido a una petición anterior, y por tanto sería necesario tener que encontrarlo de nuevo. Esto puede provocar inanición, es decir que unas peticiones se resuelvan rápidamente mientras que otras permanezcan buscando al propietario mucho más tiempo.

Para solucionar este problema proponemos detectar y evitar la inanición de un modo muy simple. Cada vez que una petición llega al nodo *home* se incrementa un contador incluido en el mensaje. Cuando este contador alcanza un cierto umbral, se marca la petición como en estado de inanición y se procede a procesarla lo antes posible. Siempre que se detecte una petición en estado de inanición se impide que el propietario del bloque solicitado por dicha petición cambie de un nodo a otro. De esta manera se garantiza que el nodo *home* sea capaz de encontrar el propietario y resolver el fallo.

### 0.4.1.2 Actualizando la cache de coherencia de primer nivel

Como comentábamos, los protocolos de coherencia directa usan la cache de coherencia de primer nivel (*L1C*\$) para evitar la indirección al nodo *home*. Esta cache almacena infomación imprecisa acerca del nodo propietario de un conjunto de bloques y puede ser actualizada de diversas maneras.

Una primera política consitiría en almacenar la identidad del último procesador que invalidó o proporcionó cada bloque. Este procesador será el propietario mientras otro no solicite permiso de escritura para ese bloque o sea reemplazado por otro bloque. A esta política la hemos llamado *Base* y no introduce tráfico extra en la red de interconexión.

Otra política alternativa, que incrementa el tráfico en la red mediante el uso de mensajes de control extra, consistiría en enviar *hints* o *pistas* a modo de mensajes de control informando del cambio de propietario a un conjunto de compartidores frecuentes, por ejemplo, los procesadores que han solicitado el bloque con anterioridad o han fallado en la predicción. A esta política la hemos llamado *Hints*. Particularmente, hemos implementado dos políticas de *hints*. La primera de ellas, *Hints-FS* (*Frequent Sharers*), añade un código de compartición junto al que ya acarrea el protocolo, el cual almacena la identidad de todos los procesadores que han solicitado cada bloque. De este modo, ante un cambio de

propietario, se envían mensajes de *hint* a todos estos nodos informando acerca del cambio. Como esta propuesta requiere una cantidad de memoria extra considerable (la adición de un nuevo código de compartición), hemos propuesto un mecanismo de *hints* basado en *address signatures* [25, 122] (*Hints-AS*). Cada *signature* almacena las direcciones de los bloques para las cuales se ha predicho incorrectamente el nodo propietario. Cuando estos bloques cambian de propietario se envían *hints* a todos los núcleos del sistema. Este mecanismo mantiene información menos precisa que el anterior y, por consiguiente, genera un poco más de tráfico a cambio de reducir significativamente el área requerida.

## 0.4.2 Reducción de la sobrecarga de memoria

Como hemos comentado en la sección anterior, DiCo-CMP necesita dos estructuras que mantienen información acerca de propietario de cada bloque. Puesto que cada entrada de estas estructuras almacena solamente el tag y un puntero al propietario ( $log_2n$  bits), tienen un orden de crecimiento bajo  $-O(log_2n)$ -. El problema aparece con el código de compartición añadido a cada entrada de las caches de datos. Si este código es un full-map, el protocolo dejaría de ser escalable en cuanto al área necesaria para implementarlo. Es por ello que proponemos el uso de códigos de compartición comprimidos en DiCo-CMP.

En concreto, hemos evaluado DiCo-CMP con los códigos de compartición mostrados en la Tabla 0.2, en la que se presentan, además, el número de bits requeridos por cada campo de la información de coherencia del protocolo y el orden de crecimiento total en cuanto al área. Como todos los protocolos de coherencia directa precisan de las caches de coherencia, el menor orden de crecimiento será  $O(log_2n)$ .

| Tabla 0.2: Bits rec | iueridos para a | ilmacenar la  | a inf | ormación  | de co  | herencia. |

|---------------------|-----------------|---------------|-------|-----------|--------|-----------|

| 10010 0.2. DIG 100  | fuctions bain t | illiaccital i | иши   | OfficeCon | ac co. | icicicia. |

| Protocolo                                                 | Código de<br>Compartición                                               | Bits cache L1<br>y cache L2                                                                                        | Bits L1C\$<br>y L2C\$                                                                                      | Orden                                             |

|-----------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| DiCo-FM<br>DiCo-CV-K<br>DiCo-LP-P<br>DiCo-BT<br>DiCo-NoSC | Full-map<br>Coarse vector<br>Limited pointers<br>Binary Tree<br>Ninguno | $ \begin{array}{c} n \\ \frac{n}{K} \\ 1 + P \times log_2 n \\ \lceil log_2(1 + log_2 n) \rceil \\ 0 \end{array} $ | log <sub>2</sub> n<br>log <sub>2</sub> n<br>log <sub>2</sub> n<br>log <sub>2</sub> n<br>log <sub>2</sub> n | $O(n)$ $O(n)$ $O(log_2n)$ $O(log_2n)$ $O(log_2n)$ |

DiCo-FM implementa un código de compartición preciso (full-map). DiCo-CV-K reduce el tamaño del código de compartición usando un coarse vector [45], en el que cada bit representa un grupo de K nodos, en lugar de sólo uno. Aunque reduce el tamaño, su orden de crecimiento sigue siendo O(n). Concretamente usamos un valor de K igual a 2. DiCo-LP-P usa un esquema de punteros limitados (limited pointer [26]), en el que se almacenan un número limitado de punteros que representan a los primeros compartidores. Cuando el número de compartidores es mayor que el número de punteros se envían las invalidaciones a todos los nodos del sistema. Este esquema crece en orden  $O(log_2n)$ . Concretamente usamos un valor de P igual a 1. DiCo-BT usa un código de compartición basado en un árbol binario, o binary tree [1], en el que los nodos son conceptualmente agrupados de manera recursiva en grupos de dos elementos, formando así un árbol binario. La información que se almacena en el código de compartición consiste en el menor nivel del árbol que abarca todos los compartidores. Este código de compartición requiere sólo 3 bits en un CMP de 16 nodos. Por último, DiCo-NoSC (no sharing code) no emplea ningún código de compartición y por tanto envía las invalidaciones a todos los nodos del sistema ante un fallo de escritura para un bloque con más de un compartidor. Aunque es el esquema que más tráfico genera, tiene la ventaja de que no requiere modificar la estructura de las caches de datos.

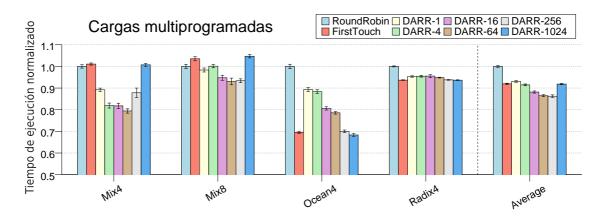

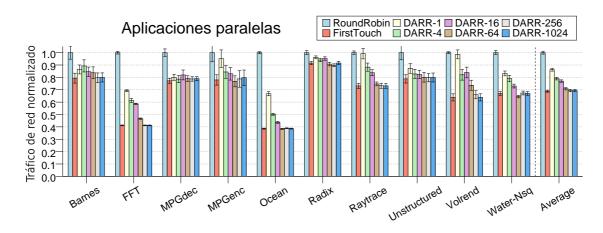

### 0.4.3 Resultados

En esta sección comparamos DiCo-CMP con otros protocolos existentes tanto en la literatura como en los multiprocesadores comerciales: *Hammer* [92], *Directorio* [38] y *Token* [78]. Sus características, junto con las de los protocolos de coherencia directa (*DiCo*), están resumidas en la Tabla 0.3. En particular, en esta sección mostramos los resultados para la implementación de DiCo-CMP que usa un mecanismo de *hints* por medio de *address signatures* y que emplea los diferentes tipos de códigos de compartición presentados en la sección anterior.

En primer lugar mostramos resultados referentes a la sobrecarga de memoria, después las reducciones en el tráfico de red y, por último, el impacto final en el tiempo de ejecución de las aplicaciones.

### 0.4.3.1 Sobrecarga de memoria

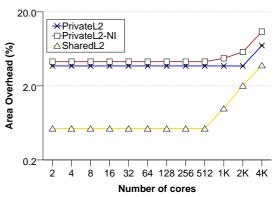

La Figura 0.10 muestra la sobrecarga de memoria de los protocolos evaluados. Esta sobrecarga se muestra variando el número de nodos del sistema desde 2

|            | Broadcast | Indirección |

|------------|-----------|-------------|

| Hammer     | Sí        | Sí          |

| Token      | Sí        | No          |

| Directorio | No        | Sí          |

| DiCo       | No        | No          |

Tabla 0.3: Resumen de los protocolos evaluados.

Figura 0.10: Sobrecarga del área de directorio en  $mm^2$  en función del número de nodos.